# Supertex inc.

## **3-Channel LED Array Driver IC**

#### Features

- Integrated 200V, 25Ω (typ.) MOSFETs

- Programmable output current to 80mA per channel

- TTL compatible PWM dimming inputs

- 3-Phase synchronous operation

- Leading edge blanking

- Short circuit protection with skip mode

- Over-temperature protection

#### **Applications**

- LCD panel backlighting

- DLP RPTV or projector LED engine driver

- RGB decorative lighting

- General LED lighting

### **General Description**

The HV9980 is a fully integrated 3-channel peak-current PWM controller for driving buck converters in constant output current mode. It is optimized for use with a large array of 20~80mA LED strings, where multiple HV9980 ICs are used sharing a common clock and a common reference voltage.

Both the clock and the voltage reference are external to the HV9980 for improved output current accuracy and uniform

illumination. The output currents are programmed by controlling peak source current in each of the three internal 200V,  $25\Omega$  switching MOSFETs.

The peak current is detected by monitoring voltage at external sense resistors connected to RSENSE1-3. The switching MOSFET is turned off when the corresponding current sense signal exceeds the reference voltage applied at REF1-3 (in the case of normal output signal polarity). Beginning of the next switching cycle is determined by the external clock signal received at the CLK input. All three channels operate at a switching frequency of 1/6 of the external clock frequency and positioned 120° out-of-phase for the purpose of input and output ripple current reduction. Each channel is protected from an output short circuit condition. When an over-current condition is detected in the output switch (RSENSE1-3), the corresponding channel shuts down for 200us. HV9980 recovers automatically, when the short circuit condition is removed. Each current sense input (CS1-CS3) is equipped with a leading edge blanking delay to prevent false triggering of the current sense comparators due to circuit parasitics.

Over-temperature protection is included to prevent destructive failures due to over-heating. Programmable slope compensation is available at each CS input. AGND and PGND1-3 must be tied together on the printed circuit board. VDD1-3 must be also connected together on the PCB.

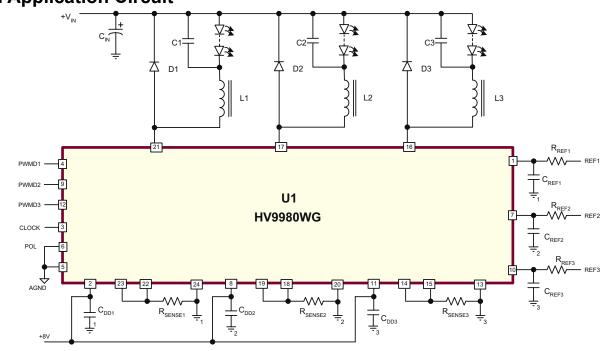

## **Typical Application Circuit**

## HV9980

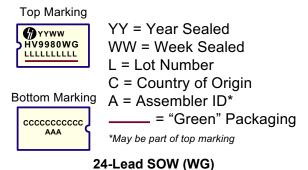

## **Ordering Information**

|                                   | Package Option                                                        |  |  |  |  |  |  |

|-----------------------------------|-----------------------------------------------------------------------|--|--|--|--|--|--|

| Device                            | 24-Lead SOW<br>15.40x7.50 body<br>2.65mm height (max)<br>1.27mm pitch |  |  |  |  |  |  |

| HV9980                            | HV9980WG-G                                                            |  |  |  |  |  |  |

| -G indicates package is RoHS comp | liant ('Green')                                                       |  |  |  |  |  |  |

| Inter                             |                                                                       |  |  |  |  |  |  |

## **Absolute Maximum Ratings**

| Parameter                                  | Value                        |

|--------------------------------------------|------------------------------|

| Supply voltage, V <sub>DD</sub>            | -0.3V to +10V                |

| Drain1-3 outputs                           | -0.3V to +200V               |

| CS1-3 inputs                               | -0.3V to +5.0V               |

| Other inputs and outputs                   | -0.3V to V_{_{\rm DD}}       |

| Supply current, I <sub>DD</sub>            | +10mA                        |

| Power dissipation ( $T_A = +25^{\circ}C$ ) | 1300mW                       |

| Thermal impedance $(\theta_{JA})$          | 60°C/W                       |

| Operating ambient temperature range        | -40°C to +85°C               |

| Operating junction tomograture range       | -40°C to +125°C <sup>1</sup> |

| Operating junction temperature range       | -40°C to +150°C <sup>2</sup> |

| Storage temperature range                  | -65°C to +150°C              |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. All voltages referenced to ground.

#### Notes:

- 1. Operation out of this range will not guarantee electrical characteristics described in this datasheet.

- 2. Operation out of this range will be destructive to the IC.

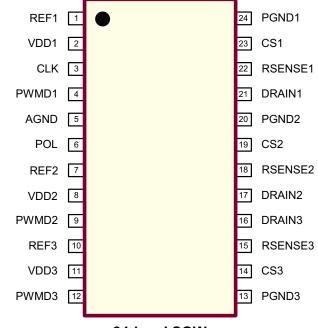

## **Pin Configuration**

## **Product Marking**

#### **Electrical Characteristics** (The specifications are at $T_4 = 25^{\circ}$ C and $V_{pp} = 8.0V$ , unless otherwise noted.)

| Sym                                                                          | Parameter                               | Min | Тур | Max | Units | Conditions |                                                                            |  |  |  |  |

|------------------------------------------------------------------------------|-----------------------------------------|-----|-----|-----|-------|------------|----------------------------------------------------------------------------|--|--|--|--|

| Supply Input (VDD1 - VDD3)                                                   |                                         |     |     |     |       |            |                                                                            |  |  |  |  |

| V <sub>DD(UVLO)</sub>                                                        | V <sub>DD</sub> undervoltage threshold  | *   | -   | -   | 5.3   | V          | VDD falling                                                                |  |  |  |  |

| $\Delta V_{DD(UVLO)}$                                                        | V <sub>DD</sub> undervoltage hysteresis | -   | -   | 500 | -     | mV         |                                                                            |  |  |  |  |

| I <sub>DD</sub>                                                              | Operating supply current                | *   | -   | -   | 3.0   | mA         | Total of VDD1 - VDD3                                                       |  |  |  |  |

| High Voltage Switches (DRAIN1 - RSENSE1, DRAIN2 - RSENSE2, DRAIN3 - RSENSE3) |                                         |     |     |     |       |            |                                                                            |  |  |  |  |

| V <sub>BR</sub>                                                              | Breakdown voltage                       | *   | 210 | -   | -     | V          |                                                                            |  |  |  |  |

| R <sub>on</sub>                                                              | On-resistance                           | -   | -   | 25  | 45    | Ω          | I <sub>DRAIN</sub> = 50mA, V <sub>RSENSE</sub> = 0V                        |  |  |  |  |

| I <sub>SAT</sub>                                                             | DRAIN saturation current                | *   | 200 | -   | -     | mA         | $V_{\text{DRAIN}} = 120 \text{V}, \text{V}_{\text{RSENSE}} = 1.3 \text{V}$ |  |  |  |  |

\* Denotes the specifications which apply over the full operating ambient temperature range of -40°C <  $T_4$  < +85°C.

## HV9980

| Sym                                                            | Parameter                          |   | Min  | Тур | Мах | Units | Conditions                                                                  |  |  |  |

|----------------------------------------------------------------|------------------------------------|---|------|-----|-----|-------|-----------------------------------------------------------------------------|--|--|--|

| Current Sense Comparators (CS1 - REF1, CS2 - REF2, CS3 - REF3) |                                    |   |      |     |     |       |                                                                             |  |  |  |

| V <sub>CS(LIM)</sub>                                           | Short circuit protection threshold | * | 1.0  | -   | 1.3 | V     |                                                                             |  |  |  |

| T <sub>SKIP</sub>                                              | Short circuit recovery delay       | - | -    | 200 | -   | μs    |                                                                             |  |  |  |

| T <sub>BLANK</sub>                                             | Leading edge blanking delay        | - | 120  | -   | 220 | ns    |                                                                             |  |  |  |

| V <sub>os</sub>                                                | Input offset voltage               | * | -7.0 | -   | 7.0 | mV    |                                                                             |  |  |  |

| T <sub>DELAY</sub>                                             | Propagation delay CS-to-DRAIN      | * | -    | -   | 150 | ns    | $V_{cs} - V_{REF} = 50 mV$                                                  |  |  |  |

| T <sub>DELAY(LIM)</sub>                                        | Shutdown delay CS-to-DRAIN         | * | -    | -   | 0.5 | μs    | $V_{\rm CS}$ = $V_{\rm CS(LIM)}$ + 100mV, $V_{\rm REF}$ > $V_{\rm CS(LIM)}$ |  |  |  |

| Oscillator Input and Frequency Divider (CLK)                   |                                    |   |      |     |     |       |                                                                             |  |  |  |

| F <sub>SW(max)</sub>                                           | Maximum switching frequency        | * | 500  | -   | -   | kHz   | f <sub>clk</sub> = 3.0MHz                                                   |  |  |  |

| K <sub>sw</sub>                                                | Frequency divider ratio            | - | -    | 6   | -   | -     | Guaranteed by design                                                        |  |  |  |

| φ <sub>2</sub>                                                 | DRAIN1-DRAIN2 phase delay          | - | -    | 120 | -   | deg   | Guaranteed by design                                                        |  |  |  |

| φ <sub>3</sub>                                                 | DRAIN1-DRAIN3 phase delay          | - | -    | 240 | -   | deg   | Guaranteed by design                                                        |  |  |  |

| T <sub>OFF</sub>                                               | CLK high time                      | - | 50   | -   | -   | ns    |                                                                             |  |  |  |

| T <sub>ON</sub>                                                | CLK low time                       | - | 50   | -   | -   | ns    |                                                                             |  |  |  |

| V <sub>CLK,HI</sub>                                            | CLK Input high                     | * | 2.0  | -   | -   | V     |                                                                             |  |  |  |

| V <sub>CLK,LO</sub>                                            | CLK Input low                      | * | -    | -   | 0.8 | V     |                                                                             |  |  |  |

|                                                                | ming (PWMD1, PWMD2, PWMD3)         |   |      |     |     |       |                                                                             |  |  |  |

| V <sub>PWMD,HI</sub>                                           | PWMD Input high                    | * | 2.0  | -   | -   | V     |                                                                             |  |  |  |

| V <sub>PWMD,LO</sub>                                           | PWMD Input low                     | * | -    | -   | 0.8 | V     |                                                                             |  |  |  |

| R <sub>PWMD</sub>                                              | PWMD Pull down resistance          | - | 100  | 200 | 300 | kΩ    | PWMD = 5.0V                                                                 |  |  |  |

|                                                                | Over Temperature Protection        |   |      |     |     |       |                                                                             |  |  |  |

| Т <sub>от</sub>                                                | Over temperature trip limit        | - | 125  | 140 | -   | °C    | Guaranteed by design                                                        |  |  |  |

| T <sub>HYST</sub>                                              | Temperature hysteresis             | - | -    | 60  | -   | °C    | Guaranteed by design                                                        |  |  |  |

## **Electrical Characteristics** (cont.) (The specifications are at $T_A = 25^{\circ}$ C and $V_{DD} = 8.0$ V, unless otherwise noted.)

\* Denotes the specifications which apply over the full operating ambient temperature range of  $-40^{\circ}C < T_{A} < +85^{\circ}C$ .

## HV9980

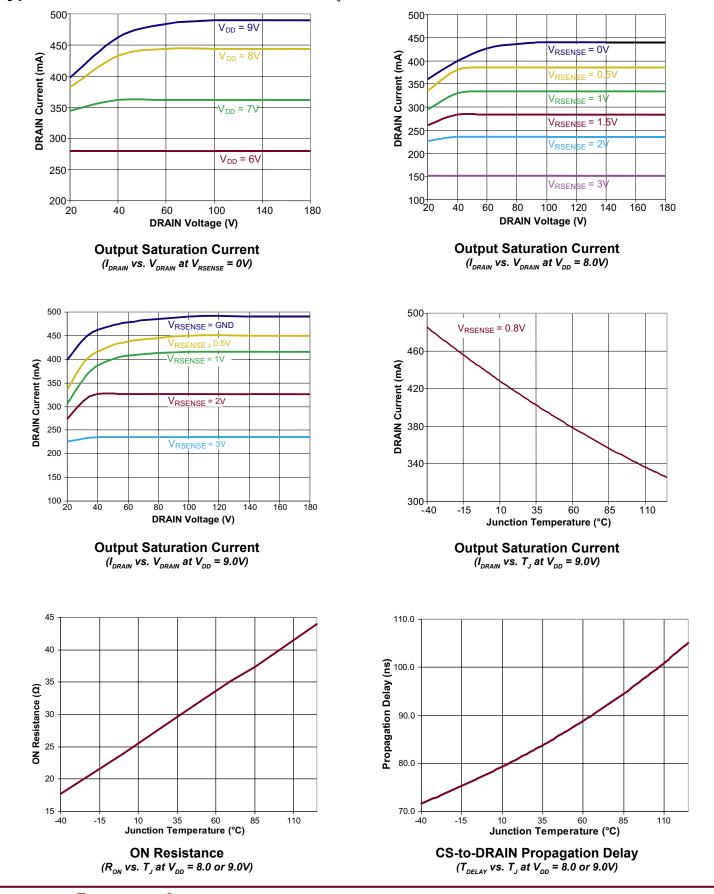

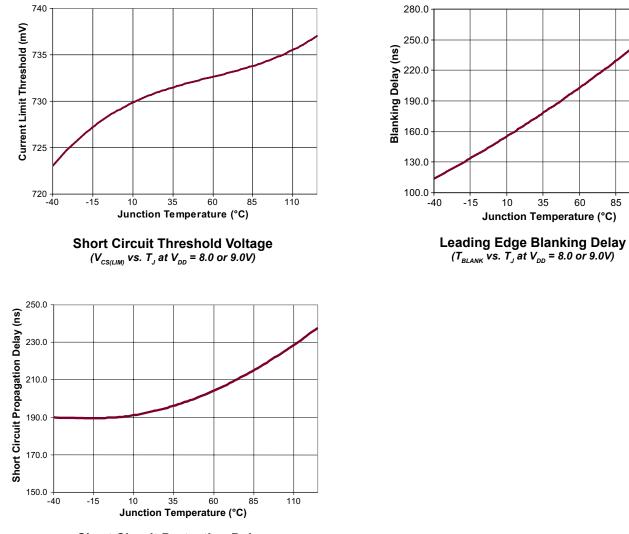

## **Typical Performance Characteristics** ( $T_{J} = 25^{\circ}C$ unless otherwise noted)

Supertex inc. • 1235 Bordeaux Drive, Sunnyvale, CA 94089 • Tel: 408-222-8888 • www.supertex.com

110

### **Typical Performance Characteristics** (cont.) ( $T_{J} = 25^{\circ}C$ unless otherwise noted)

Short Circuit Protection Delay (T<sub>DELAY(LIM)</sub> vs. T<sub>J</sub> at V<sub>DD</sub> = 8.0 or 9.0V)

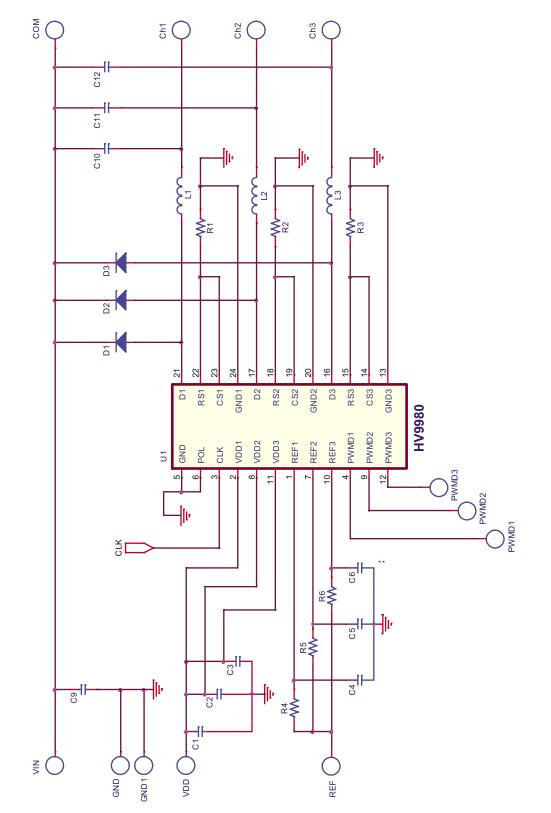

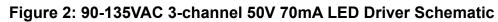

### Figure 1: 110-190VDC 3-channel 50V 70mA LED Driver Schematic

7

#### **Application Information**

#### Programming LED current and selecting L and D

The required value of the output inductor L is inversely proportional to the ripple current  $\Delta I_{o}$  in it. Setting the relative peak-to-peak ripple to 20~30% is a good practice to ensure noise immunity of the current sense comparator.

$$L = (V_{\circ} \bullet T_{oFF}) / \Delta I_{\circ} = (V_{\circ} \bullet [1 - D]) / f_{s} \Delta I_{\circ}$$

(1)

$V_o$  is the forward voltage of the LED string,  $f_s$  is the switching frequency,  $D = V_o/V_{IN}$  is the switching duty cycle.

The output current in the LED string  $(I_{o})$  is calculated as:

$$I_{o} = (V_{REF} / R_{SENSE}) - 1/2 \cdot \Delta I_{o}$$

<sup>(2)</sup>

where V<sub>REF</sub> is the voltage at REF1-3, and R<sub>SENSE</sub> is the current sense resistor at RSENSE1-3. (The ripple current introduces a peak-to-average error in the output current setting that needs to be accounted for.)

Adding a filter capacitor across the LED string can reduce the output current ripple yielding a reduced value of L. However, one must keep in mind that the peak-to-average current error is affected by the variation of the input and output voltage. Therefore, the line and load regulation of the LED current might be sacrificed at large ripple current in L.

Another important aspect of designing an LED driver with the HV9980 is related to certain parasitic elements of the circuit, including distributed coil capacitance of L1, junction capacitance and reverse recovery of the rectifier diode D1, capacitance of the printed circuit board traces  $C_{PCB}$  and output capacitance  $C_{DRAIN}$  of the controller itself. These parasitic elements affect the efficiency of the switching converter and could potentially cause false triggering of the current sense comparator if not properly managed. Minimizing these parasitics is essential for efficient and reliable operation of the HV9980.

Coil capacitance of inductors is typically provided in the manufacturer's data books either directly or in terms of the self-resonant frequency (SRF).

SRF =

$$1/(2\pi\sqrt{L \cdot C_i})$$

where *L* is the inductance value, and *C<sub>L</sub>* is the coil capacitance.) Charging and discharging this capacitance every switching cycle causes high-current spikes in the LED string. Therefore, connecting a small capacitor  $C_o$  (~10nF) is recommended to bypass these spikes.

Using an ultra-fast rectifier diode for D1 is recommended to achieve high efficiency and reduce the risk of false triggering of the current sense comparator. Using diodes with shorter reverse recovery time  $t_{rr}$  and lower junction capacitance  $C_J$  achieves better performance. The reverse voltage rating  $V_R$  of the diode must be greater than the maximum input voltage of the LED lamp.

The total parasitic capacitance present at the DRAIN output of the HV9980 can be calculated as:

$$C_{P} = C_{DRAIN} + C_{PCB} + C_{L} + C_{J}$$

(3)

When the switch turns on, the capacitance  $C_{\rho}$  is discharged into the DRAIN output of the IC. The discharge current is limited to about 300mA typically. However, it may become lower at increased junction temperature. The duration of the leading edge current spike can be estimated as:

$$T_{SPIKE} = [(V_{IN} \bullet C_P) / I_{SAT}] = t_{rr}$$

(4)

In order to avoid false triggering of the current sense comparator,  $C_{p}$  must be minimized in accordance with the following expression:

$$C_{P} < [I_{SAT} \bullet (T_{BLANK(MIN)} - t_{rr})] / V_{IN(MAX)}$$

(5)

where  $T_{_{BLANK(MIN)}}$  is the minimum blanking time of 120ns, and  $V_{_{IN(MAX)}}$  is the maximum instantaneous input voltage.

#### Layout Considerations

The HV9980 provides three independent power ground connections PGND1-3 for each channel. The PGND pins must be wired together on the printed circuit board (PCB). To minimize interference between the channels, the PGND pins should be wired to the negative terminal of the input filter capacitor CIN using separate tracks. All four power supply inputs VDD, VDD1-3 must be connected together on the PCB also.

Although in many layout arrangements wiring the reference pins REF1-3 together is acceptable, further reduction of the "cross-talk" between the channels is possible by adding low-pass RC filters with the filter capacitors referenced to the corresponding PGND pins. These filters composed from R<sub>REF1-3</sub> and C<sub>REF1-3</sub> are shown in the Typical Application Circuit diagram.

## **Pin Description**

| Pin # | Name    | Description                                                                                                                                                                      |

|-------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | REF1    | Voltage reference inputs to the current sense comparators. For best noise immunity, connect an                                                                                   |

| 7     | REF2    | RC filter at each of these pins referenced to the corresponding PGND pin. The filter can consist                                                                                 |

| 10    | REF3    | of a 1.0nF low impedance capacitor and a 1.0k $\Omega$ resistor.                                                                                                                 |

| 2     | VDD1    | Power supply inputs. For best noise immunity, bypass each of these pins to the corresponding                                                                                     |

| 8     | VDD2    | PGND pin with a 0.1uF low impedance capacitor. The VDD pins must be tied together on the                                                                                         |

| 11    | VDD3    | PCB.                                                                                                                                                                             |

| 3     | CLK     | Input to an external clock signal common to all three channels. Programs the switching frequency of the power MOSFET outputs at 1/6 of the clock signal frequency.               |

| 4     | PWMD1   |                                                                                                                                                                                  |

| 9     | PWMD2   | Dedicated PWM dimming inputs for each individual LED string driver channel.                                                                                                      |

| 12    | PWMD3   |                                                                                                                                                                                  |

| 5     | AGND    | Common return pin for CLK, POL and PWMD inputs.                                                                                                                                  |

| 6     | POL     | Must be connected to AGND.                                                                                                                                                       |

| 13    | PGND3   |                                                                                                                                                                                  |

| 20    | PGND2   | Power return terminals for corresponding DRAIN outputs. The PGND and AGND pins must be tied together on the PCB.                                                                 |

| 24    | PGND1   |                                                                                                                                                                                  |

| 14    | CS3     | Signal inputs to the current sense comparators. Connect these pins to the corresponding                                                                                          |

| 19    | CS2     | RSENSE outputs directly when the slope compensation feature is not used. When the slope compensation is needed, connect a capacitor between each RSENSE and its corresponding CS |

| 23    | CS1     | pin, and connect a resistor between each CS pin and VDD.                                                                                                                         |

| 15    | RSENSE3 |                                                                                                                                                                                  |

| 18    | RSENSE2 | Open source outputs of the switching power MOSFETs. Connect a current sense resistor between each of the RSENSE pins and its corresponding PGND pin.                             |

| 22    | RSENSE1 |                                                                                                                                                                                  |

| 16    | DRAIN3  |                                                                                                                                                                                  |

| 17    | DRAIN2  | Open drain outputs of the switching power MOSFETs.                                                                                                                               |

| 21    | DRAIN1  |                                                                                                                                                                                  |

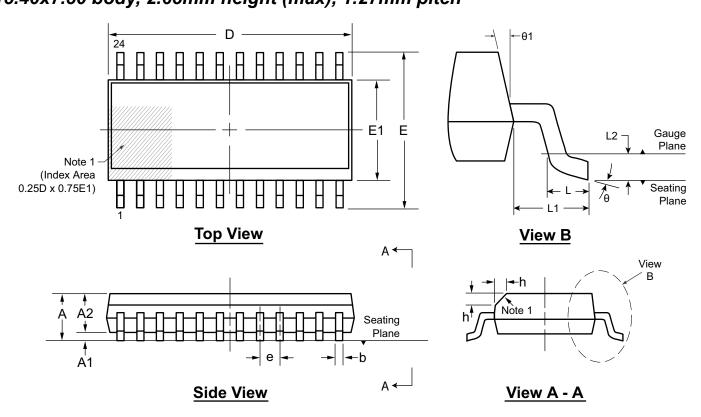

## 24-Lead SOW (Wide Body) Package Outline (WG) 15.40x7.50 body, 2.65mm height (max), 1.27mm pitch

Note:

1. This chamfer feature is optional. If it is not present, then a Pin 1 identifier must be located in the index area indicated. The Pin 1 Identifier can be: a molded mark/identifier; an embedded metal marker; or a printed indicator.

| Symbo             | ol  | Α     | A1   | A2    | b    | D      | Е      | E1    | е                   | h    | L    | L1                   | L2         | θ          | θ1              |

|-------------------|-----|-------|------|-------|------|--------|--------|-------|---------------------|------|------|----------------------|------------|------------|-----------------|

| Dimension<br>(mm) | MIN | 2.15* | 0.10 | 2.05  | 0.31 | 15.20* | 9.97*  | 7.40* | 0.25<br>1.27<br>BSC | 0.25 | 0.40 |                      | <b>0</b> 0 | <b>5</b> ° |                 |

|                   | NOM | -     | -    | -     | -    | 15.40  | 10.30  | 7.50  |                     | -    | -    | 1.40 0.25<br>REF BSC | -          | -          |                 |

|                   | MAX | 2.65  | 0.30 | 2.55* | 0.51 | 15.60* | 10.63* | 7.60* |                     | 0.75 | 1.27 |                      | 200        | <b>8</b> 0 | 15 <sup>0</sup> |

JEDEC Registration MS-013, Variation AD, Issue E, Sep. 2005.

\* This dimension is not specified in the original JEDEC drawing. The value listed is for reference only.

Drawings are not to scale.

Supertex Doc. #: DSPD-24SOWWG, Version D090408.

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <u>http://www.supertex.com/packaging.html</u>.)

Supertex inc. does not recommend the use of its products in life support applications, and will not knowingly sell them for use in such applications unless it receives an adequate "product liability indemnification insurance agreement." Supertex inc. does not assume responsibility for use of devices described, and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions and inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications refer to the Supertex inc. website: http://www.supertex.com.

©2008 Supertex inc. All rights reserved. Unauthorized use or reproduction is prohibited.