# DESCRIPTION

The MP1038 is a fixed operating frequency inverter controller that controls four external N-Channel power MOSFETs in a full-bridge configuration. The inverter is designed to power one or more cold cathode fluorescent lamps (CCFL) to backlight liquid crystal displays. Its full-bridge architecture converts unregulated DC input voltages to the nearly pure sine waves required to ignite and operate CCFL.

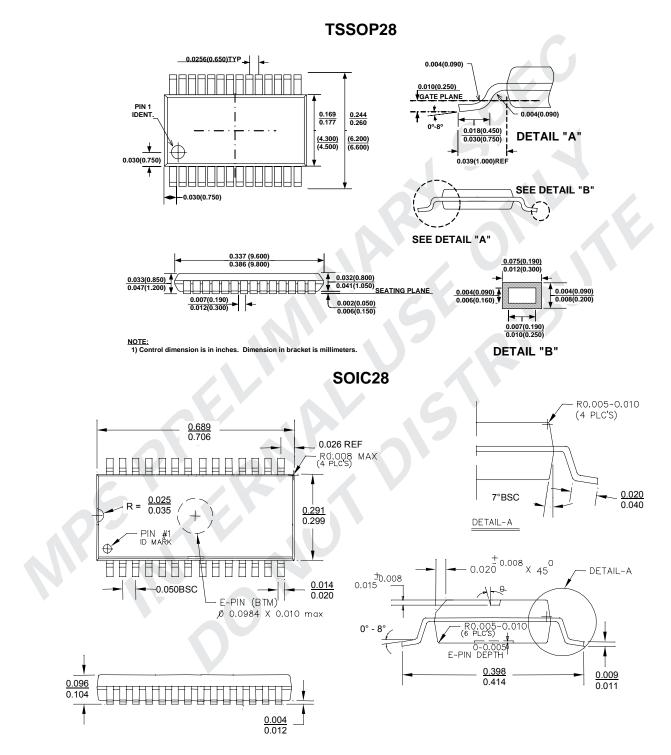

For reliable lamp ignition, the operating frequency is set by an external resistor and during startup, is temporarily swept toward the unloaded resonant frequency of the tank. The built-in burst oscillator can be synchronized with an external clock to minimize display scan interference. Burst mode or analog mode dimming is controlled with an external analog signal. Built-in fault management features include an open lamp regulator, a transformer secondary peak current regulator, and a dual-mode fault timer. The secondary over-current timeout can be shortened with external components. Built-in current limits for the external switches protect against inadvertent shorts. The MP1038 is available in TSSOP28 and SOIC28 packages.

# **FEATURES**

- Controls Four External, Low Cost, N-Channel MOSFETs

- Fixed Operating Frequency

- Input Voltage Range of 10V to 32V

- Lamp Current and Voltage Regulation

- Full-Wave Sense Amp

- Analog and Burst Mode Dimming Control

- Integrated Burst Mode Oscillator and Modulator

- Soft On and Soft Off Burst Envelope

- Open Lamp Protection

- Secondary Over-Current Protection

- Dual-mode, Fault Timer

- Thermal Shutdown with Hysteresis

- Available in TSSOP28 and SOIC28 Packages

# APPLICATIONS

- Desktop LCD Flat Panel Displays

- Flat Panel Video Displays

- LCD TVs and Monitors

**MPS**", "MPS", "Monolithic Power Systems", and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc. The MP1038 is covered by US Patents 6,683,422, 6,316,881, and 6,114,814. Other Patents Pending.

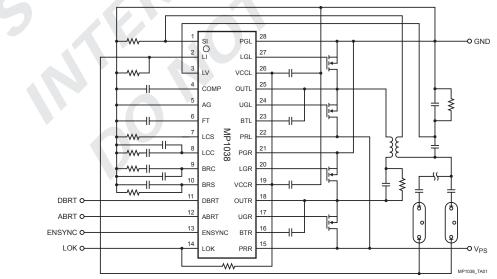

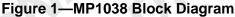

# TYPICAL APPLICATION

#### MP1038 – FULL BRIDGE CCFL CONTROLLER

PRELIMINARY RELEASE - MPS CONFIDENTIAL

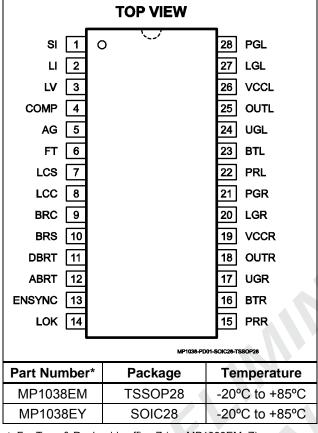

# PACKAGE REFERENCE

\* For Tape & Reel, add suffix -Z (eg. MP1038EM-Z) For Lead Free, add suffix -LF (eg. MP1038EM-LF-Z)

# ABSOLUTE MAXIMUM RATINGS (1)

| Input Voltage V <sub>PRR</sub> , V <sub>PRL</sub> | 35V            |

|---------------------------------------------------|----------------|

| Logic Inputs                                      |                |

| Junction Temperature                              | 150°C          |

| Power Dissipation                                 | 0.6W           |

| Junction Temperature                              | 150°C          |

| Lead Temperature (Solder)                         | 260°C          |

| Operating Frequency                               |                |

| Storage Temperature                               | 55°C to +150°C |

|                                                   |                |

# Recommended Operating Conditions (2)

| 10V to 32V   |

|--------------|

| . 0V to 1.2V |

| . 0V to 1.2V |

| .0V to 5.0V  |

| z to 100kHz  |

| 60kHz        |

| C to + 85°C  |

|              |

#### Thermal Resistance <sup>(3)</sup>

| Θ <sub>JA</sub> (TSSOP28) | 82°C/W |

|---------------------------|--------|

| Θ <sub>JC</sub> (TSSOP28) | 20°C/W |

| Θ <sub>JA</sub> (SOIC28)  | 60°C/W |

| Θ <sub>JC</sub> (SOIC28)  | 30°C/W |

Notes:

- 1) The device is not guaranteed to function outside of its operating conditions.

- Exceeding these ratings may damage the device.

Measured on approximately 1" square of 1 oz copper.

# **ELECTRICAL CHARACTERISTICS**

$V_{PRR} = V_{PRL} = 17.5V$ ,  $V_{BRC} = V_{LCC} = GND$ ,  $T_A = 25C$ , unless otherwise noted.

| Parameter                   | Symbol                 | Condition          | Min | Тур  | Max | Units |

|-----------------------------|------------------------|--------------------|-----|------|-----|-------|

| Output                      |                        |                    |     |      |     | •     |

| Gate Pull-Down              | R <sub>GD</sub>        |                    |     | 1.6  | 2.3 | Ω     |

| Gate Pull-Up                | R <sub>GU</sub>        |                    |     | 34   | 45  | Ω     |

| Damper On Resistance        | R <sub>on</sub>        |                    |     | 1.1  | 1.5 | kΩ    |

| ENSYNC                      |                        |                    | •   |      |     |       |

| Threshold                   | V <sub>TH</sub>        |                    |     | 1.35 | 1.5 | V     |

| Hysteresis                  | V <sub>TH_HYS</sub>    |                    |     | 0.3  |     | V     |

| Sync Timing                 |                        |                    | •   |      |     |       |

| Sync Minimum Pulse Width    | t <sub>SYNC(MIN)</sub> |                    |     | 1    |     | μs    |

| Sync Maximum Pulse Width    | t <sub>SYNC(MAX)</sub> |                    |     | 10   |     | μs    |

| Sync Rate                   | f <sub>SYNC</sub>      |                    |     | 200  |     | Hz    |

| DBRT Logic Input Threshold  | V <sub>TH</sub>        | $V_{BRS} = V_{CC}$ | 2.0 | 2.1  | 2.2 | V     |

| DBRT Logic Input Hysteresis | V <sub>TH_HYS</sub>    | $V_{BRS} = V_{CC}$ |     | 0.4  |     | V     |

# **ELECTRICAL CHARACTERISTICS** (continued) $V_{PRR} = V_{PRL} = 17.5V, V_{BRC} = V_{LCC} = GND, T_A = 25C$ , unless otherwise noted.

| Parameter                                      | Symbol                           | Condition                 | Min   | Тур  | Max   | Units |

|------------------------------------------------|----------------------------------|---------------------------|-------|------|-------|-------|

| Brightness Control Range                       |                                  |                           | •     |      |       |       |

| DBRT Full Scale                                | V <sub>DBRT</sub>                |                           |       | 1.2  |       | V     |

| ABRT Full Scale                                | V <sub>ABRT</sub>                |                           |       | 1.2  |       | V     |

| Burst Rate Generator                           | I.                               |                           |       |      | 1     | 1     |

| Source Current                                 | I <sub>SRC(BRS)</sub>            | V <sub>BRS</sub> = 2V     | 120   | 140  | 165   | uA    |

| Lower Threshold                                | V <sub>V(BRS)</sub>              |                           | 2.3   | 2.4  | 2.5   | V     |

| Upper Threshold                                | V <sub>P(BRS)</sub>              |                           | 3.4   | 3.5  | 3.6   | V     |

| Supply Current                                 |                                  |                           |       |      | 1     | 1     |

| Supply Current (enabled)                       | I <sub>PR</sub>                  |                           |       | 1.4  | 2     | mA    |

| Supply Current (disabled)                      | I <sub>PR</sub>                  |                           |       | 1    | 10    | μA    |

| Operating Frequency                            | f <sub>0</sub>                   | R3 = 100kΩ                |       | 50   |       | KHz   |

| Accuracy of f <sub>0</sub>                     |                                  |                           |       | 3    |       | %     |

| Sweep Range                                    | F <sub>MAX</sub> /f <sub>0</sub> |                           |       | 1.6  |       |       |

| Control Input Current                          | ILCC                             |                           |       | -1   |       | μA    |

| Frequency Set Voltage                          | V <sub>LCS</sub>                 |                           | 1.15  | 1.2  | 1.25  | V     |

| Lamp Current Feedback                          |                                  |                           |       |      |       | 1     |

| Magnitude                                      | V <sub>LI</sub>                  | V <sub>ABRT</sub> > 1.2 V | 1.134 | 1.20 | 1.266 | V     |

|                                                |                                  | V <sub>ABRT</sub> = 0 V   | 0.36  | 0.40 | 0.44  | V     |

| Sine Equivalent                                | V <sub>LI</sub>                  | V <sub>ABRT</sub> > 1.2 V |       | 1.33 |       | Vrms  |

| Accuracy                                       | V <sub>LI</sub>                  |                           |       | 3    |       | %     |

| Input Resistance                               |                                  | V <sub>LI</sub> < 0 V     |       | 62   |       | kΩ    |

| Open Lamp Voltage Feedback<br>Threshold (peak) | V <sub>TH(LV)</sub>              | ~7                        | 1.164 | 1.20 | 1.236 | V     |

| Secondary Peak Current Threshold               | V <sub>TH(SI)</sub>              |                           | 1.164 | 1.20 | 1.236 | V     |

| Fault Timer                                    |                                  |                           |       |      | 1     |       |

| Threshold                                      | V <sub>t(FT)</sub>               |                           | 1.164 | 1.20 | 1.236 | V     |

| Sink Current                                   |                                  |                           |       | -1   |       | μA    |

| Open lamp source current                       | I <sub>SO(FT)+</sub>             |                           |       | 1    |       | μA    |

| Secondary over-current source current          | I <sub>SP(FT)+</sub>             |                           |       | 55   |       | μA    |

| Comp                                           |                                  |                           |       |      |       |       |

| Clamp Voltage                                  | V <sub>COMP</sub>                |                           |       | 0.56 |       | V     |

| Reference Current                              | I <sub>COMP+</sub>               |                           | 15    | 20   |       | μA    |

| Decay Current                                  | I <sub>COMP-</sub>               | End of Burst              | 50    | 60   |       | μA    |

| Output (VCCR and VCCL)                         |                                  | •                         | ·     |      | •     |       |

| Voltage                                        | V <sub>CC</sub>                  |                           | 5.7   | 6.0  | 6.3   | V     |

| Current                                        | I <sub>CC</sub>                  |                           |       | 5    |       | mA    |

| Shutdown Temperature                           | T <sub>SD</sub>                  |                           |       | 140  |       | С     |

| Hysteresis                                     | -                                |                           |       | 20   |       | С     |

# **PIN FUNCTIONS**

#### For TSSOP28 and SOIC28 devices

| Pin # | Name   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | SI     | Secondary Current Feedback Input. Connect a current sense resistor from the cold end of the secondary winding to ground. Connect this pin to the junction of the resistor and the secondary winding. If the voltage at SI exceeds +1.2V, a pulse of current will pull down on the COMP pin to attempt to regulate the secondary current and the Fault Timer will be started.                                                                    |

| 2     | L      | Lamp Current Feedback Input. Connect this pin to the cold end of the lamp and shunt a sense resistor to ground. The sense amplifier will sink a current from the COMP pin proportional to the absolute value of the voltage at this pin. (In regulation the average of the absolute value of the voltage at this pin is determined by the voltage at the ABRT pin).                                                                             |

| 3     | LV     | Lamp Voltage Feedback Input. Connect a capacitive voltage divider from the hot end of the lamp to ground. Connect this pin to the tap on the divider and shunt a bias resistor to ground. If the voltage at LV exceeds +1.2 V, a pulse of current will pull down on the COMP pin to attempt to regulate the lamp voltage and the Fault Timer will be started.                                                                                   |

| 4     | COMP   | Feed back Compensation Node. Connect a compensation capacitor from this pin to ground.                                                                                                                                                                                                                                                                                                                                                          |

| 5     | AG     | Analog Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6     | FT     | Fault Timing. Connect a timing capacitor from this pin to AG to set the fault timeout period.                                                                                                                                                                                                                                                                                                                                                   |

| 7     | LCS    | Lamp operating Clock Set. Connect a resistor from this pin to AG. This resistor sets the operating frequency of the MP1038.                                                                                                                                                                                                                                                                                                                     |

| 8     | LCC    | Lamp Clock Control. LCC provides compensation when the operating clock is swept in order to strike the lamp. Connect a resistor in series with a capacitor from LCC to AG. Connect a smaller capacitor directly from LCC to AG. Connect only a single capacitor to AG, if some sweeping of the operating clock can be tolerated during open lamp conditions. Connect LCC to AG to force the operating clock to the selected value at all times. |

| 9     | BRC    | Burst Repetition rate Control. BRC provides compensation when the burst repetition rate is to be synchronized to an external clock. Connect a resistor in series with a capacitor from BRC to AG. Connect a smaller capacitor directly from BRC to AG. If the burst repetition rate is not to be synchronized to an external clock, connect BRC to AG.                                                                                          |

| 10    | BRS    | Burst Repetition rate Setting. If the burst repetition rate is to be synchronized to an external clock, connect a capacitor from BRS to AG. If the burst rate generator is free-run and not be synchronized with an external clock, connect a resistor in parallel with a capacitor from BRS to AG. If the burst is to be controlled by an external logic signal, connect BRS to VCC and apply the logic signal to the DBRT pin.                |

| 11    | DBRT   | Burst-Mode (Digital) Brightness Control Input. The voltage range of 0V to 1.2V at DBRT linearly sets the burst-mode duty cycle from minimum 10% to 100%. If burst dimming is not used tie DBRT to VCC.                                                                                                                                                                                                                                          |

| 12    | ABRT   | Analog Brightness Control Input. The voltage range of 0V to 1.2V at ABRT sets 3:1 dimming range for the lamp current. If analog dimming is not used, tie ABRT to VCC.                                                                                                                                                                                                                                                                           |

| 13    | ENSYNC | Enable and Sync Composite Input. Pull ENSYNC high to turn on the MP1038, pull ENSYNC low to turn it off. To synchronize the burst repetition rate to an external clock, apply the synchronizing clock signal with low-going pulse width of 1-10us to this pin. Once the MP1038 has aligned the burst oscillator to the sync signal, each burst will start at the low-going edge of the sync pulse.                                              |

| 14    | LOK    | Lamp OK Flag Output (open drain). Connect this pin to a pull-up resistor to logic high. This pin will not be activated during normal operation (including burst mode) nor when the MP1038 is disabled. This pin will be pulled low when a fault (open lamp or secondary over-current) is detected.                                                                                                                                              |

| 15    | PRR    | Input Power Rail, Right-Side. Connect PRR directly to the drain of the high-side, right-side, external power MOSFET.                                                                                                                                                                                                                                                                                                                            |

# PIN FUNCTIONS (continued)

For TSSOP28 and SOIC28 devices

| Pin # | Name | Description                                                                                                                                             |

|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16    | BTR  | Output Bootstrap, Right-Side. BTR provides gate bias for the right-side high-side MOSFET. Connect a capacitor from BTR to OUTR.                         |

| 17    | UGR  | High-Side MOSFET Gate Output, Right-Side. Connect UGR to the gate of the high-side, right-side, external power MOSFET.                                  |

| 18    | OUTR | Bridge Output, Right-Side. Connect OUTR to the source of the right-side, high-side MOSFET and the drain of the low-side, right-side MOSFET.             |

| 19    | VCCR | Voltage Rail Output, Right-Side. VCCR allows bypassing the bias supply for the control circuitry. Bypass VCCR with a 0.47uF capacitor. Connect to VCCL. |

| 20    | LGR  | Low-Side MOSFET Gate Output, Right-Side. Connect LGR to the gate of the low-side, right-side MOSFET.                                                    |

| 21    | PGR  | Power Ground, Right-Side. Connect PGR to the source of the low-side, right-side MOSFET.                                                                 |

| 22    | PRL  | Input Power Rail, Left-Side. Connect PRL directly to the drain of the high-side, left-side, external power MOSFET.                                      |

| 23    | BTL  | Output Bootstrap, Left-Side. BTL provides gate bias for the left-side high-side MOSFET. Connect a capacitor from BTL to OUTL.                           |

| 24    | UGL  | High-Side MOSFET Gate Output, Left-Side. Connect UGL to the gate of the high-side, left-side, external power MOSFET.                                    |

| 25    | OUTL | Bridge Output, Left-Side. Connect OUTL to the source of the left-side, high-side MOSFET and the drain of the left-side, low-side MOSFET.                |

| 26    | VCCL | Voltage Rail Output, Left-Side. VCCL allows bypassing the bias supply for the control circuitry. Bypass VCCL with a 0.47uF capacitor. Connect to VCCR.  |

| 27    | LGL  | Low-Side MOSFET Gate Output, Left-Side. Connect LGL to the gate of the low-side, left-side MOSFET.                                                      |

| 28    | PGL  | Power Ground, Left-Side. Connect PGL to the source of the low-side, left-side MOSFET.                                                                   |

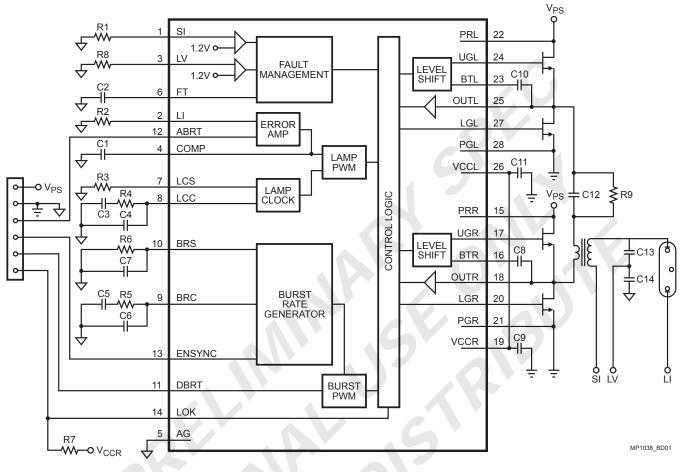

# **OPERATION**

#### **DESIGN INFORMATION**

The The MP1038 is a fixed operating frequency inverter controller specifically designed to drive a cold cathode fluorescent lamp (CCFL) used as a backlight for liquid crystal displays. Designed to run off 10 to 35V input supplies, the MP1038 can drive up to 30 lamps (150W) via four (4) external N-Channel MOSFETs. Its full bridge architecture converts unregulated DC input voltages to the nearly pure sine waves required to ignite and operate CCFLs. Operating frequency is set by an external resistor to minimize the possibility of interference with the refresh rate of the display.

To ensure ignition of the lamp, the operating frequency is swept temporarily to the unloaded resonant frequency of the tank. Regulated lamp current and maximum peak transformer secondary current are set by external resistors.

Regulated open lamp voltage is set by an external capacitive voltage divider. Soft startup of the lamp minimizes the peak transformer secondary voltage. The MP1038 implements burst mode dimming of the lamp and features soft-on-soft-off control of the lamp current envelope that is virtually independent of supply voltage.

Burst repetition rate and duty cycle can either be determined by driving the MP1038 with an external logic signal or by choosing an external resistor and capacitor to set the burst rate and modulating the duty cycle with a DC control voltage on  $D_{BRT}$ .

Loop gain is compensated for variations in supply voltage and the full-wave lamp current sense amplifier provides superior output pulse symmetry, loop response time, and phase margin.

Careful management of limit conditions provides graceful reduction of lamp power at low supply voltages but allows the loop to recover quickly from an abrupt step in supply voltage. System fault management facilities include an on-chip open-lamp regulator, a transformer secondary peak current regulator, and a dual-mode fault timer.

By regulating the peak current in the transformer secondary winding, UL1950 can be met for most systems. When the MP1038 is regulating open lamp voltage, it ignores the burst control and runs continuously to ensure either the lamp has a chance to re-ignite or the fault timer can smoothly and accurately time out. If the MP1038 detects an open lamp condition for a time that exceeds the timer interval, it will shut down until the part is turned off and then turned on again. Similarly, the MP1038 will shut down if it detects an overcurrent condition in the secondary for about 2% of the open lamp timer interval. If required, the secondary over-current timeout can be shortened with external components. On-chip current limit and thermal shutdown protect the MP1038 in case of output fault conditions. In the event that the die temperature exceeds about 140°C, the MP1038 will cease operation until the die temperature has fallen below about 120°C and then will make a normal restart.

#### FEATURE DESCRIPTION

All reference designators refer to Figure 1, unless otherwise designated.

#### **High Efficiency Operation**

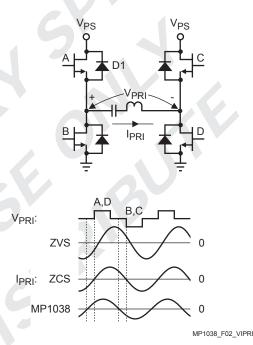

There are two major power losses in a CCFL inverter: switching loss of switches and cooper loss of the transformer winding. To reduce switching loss, Zero Current Switching (ZCS as described in US patent 6,114,814) or Zero Voltage Switching (ZVS) are commonly implemented.

As shown in Figure 2, ZCS and ZVS require primary current  $I_{PRI}$  lagging primary voltage  $V_{PRI}$ . With ZVS, since D1 can only conduct at the negative phase of  $I_{PRI}$ , the beginning of A & D conduction will only happen at the negative phase of  $I_{PRI}$ .

#### PRELIMINARY RELEASE – MPS CONFIDENTIAL

Higher phase delay will lead to higher primary RMS current and therefore higher transformer temperature. With ZCS, A & D conduction start at the zero crossing of  $I_{PRI}$ .

The MP1038 does not utilize ZVS or ZCS. It implements fast switching to reduce switching loss and operates at the condition that  $I_{PRI}$  and  $V_{PRI}$  in phase to reduce primary RMS current. Therefore, higher efficiency than ZVS or ZCS is achieved.

Figure 2—V<sub>PRI</sub> vs. I<sub>PRI</sub>

#### Brightness Control

The MP1038 can operate in four modes: Analog Mode, Burst Mode with a DC input, Burst Mode with an external PWM or Analog and Burst Mode. The four modes are dependent on the pin connections defined under Pin Functions.

Choosing the required burst repetition by an frequency can be achieved RC combination. as defined in component selection. The MP1038 has a soft-on and soft-off feature to reduce noise, when using burst mode dimming. Analog dimming and Burst dimming are independent of each other and may be used together to obtain a wider dimming range.

#### Table 1—Function Mode

| Function                                            | Pin Connection  |          |                 |                    |  |

|-----------------------------------------------------|-----------------|----------|-----------------|--------------------|--|

|                                                     | ABRT            | DBRT     | BRS             | Ratio              |  |

| Analog Mode                                         | 0 – 1.2V        | $V_{CC}$ | R6<br>C7        | 3:1                |  |

| Burst Mode<br>with DC<br>Input Voltage              | V <sub>CC</sub> | 0 – 1.2V | R6<br>C7        | 10:1               |  |

| Burst Mode<br>with External<br>Source               | V <sub>CC</sub> | PWM      | V <sub>cc</sub> | Set by<br>Customer |  |

| Analog and<br>Burst Mode                            | 0 – 1.2V        | 0 – 1.2V | R6<br>C7        | 30:1               |  |

| Analog and<br>Burst Mode<br>with External<br>Source | 0 – 1.2V        | PWM      | V <sub>cc</sub> | Set by<br>Customer |  |

Brightness Polarity

Burst: 100% duty cycle is at 1.2V Analog: 1.2V is maximum brightness

#### **Fault Protection**

<u>Open Lamp:</u> The LV pin (#3) is used to detect whether an open lamp condition has occurred. If the voltage at LV exceeds +1.2V, a pulse of current will pull down on the COMP pin to regulate the lamp voltage. The Fault Timer will be started with a 1 $\mu$ A current source injecting into C2 at the FT pin, while the fault condition persists. If the voltage at the FT pin exceeds 1.2V, then the chip will shut down.

Excessive Secondary Current (Shorted Lamp): The SI pin (#1) is used to detect whether excessive secondary current has occurred. If a fault condition occurs that increases the secondary current, then the voltage at SI will be greater than 1.2V. A pulse of current will pull down on the COMP pin to regulate the secondary current. The Fault Timer will be started with a 55µA current source injecting into C2 at the FT pin, while the fault condition persists.

#### PRELIMINARY RELEASE – MPS CONFIDENTIAL

If the voltage at the FT pin exceeds 1.2V, then the chip will shut down and needs to be re-enabled.

<u>Fault Timer</u>: The timing for the fault timer will depend on the sourcing current, as described above, and the capacitor C2 on the FT pin. The user can program the time for the voltage to rise after the chip detects a "real" fault. When a fault is triggered, then the internal voltage ( $V_{CC}$ ) will collapse from 6V to 0V. If no fault is detected a 1µA current sink will keep FT to 0V.

#### Startup

For reliable ignition of the lamp, the operating frequency is swept temporarily toward the unloaded resonant frequency of the tank during startup. This guarantees the strike voltage of the lamp at any temperature due to a resonant topology for switching the outputs and eliminates the need for external ramp timing circuits to ensure startup. Once the strike voltage is achieved, the switching frequency is gradually adjusted to the preset fixed value. The operating frequency before the lamp strikes can be swept as much as 140% of the preset frequency value.

#### Chip Enable

The chip has an ON/OFF function, which is controlled by the ENSYNC pin (#13). The enable signal goes directly to a Schmitt trigger. The chip will turn ON with an ENSYNC = High and OFF with an ENSYNC = Low.

The Burst waveform can be synchronized to an external reference clock. To do this, remove R6 and combine a low-going synchronization signal with the enable signal at the ENSYNC pin. The synchronizing pulses should be  $1\mu$ s -  $10\mu$ s wide and should occur at the desired burst repetition frequency.

# **APPLICATION INFORMATION**

#### Pin 1 (SI), R1:

<u>Secondary Short Protection:</u> The R1 is used for feedback to the SI pin to detect excessive secondary current. The value for R1 is calculated as 1.2V divided by the secondary peak current.

#### Pin 2 (LV): C13, C14 and R8:

<u>Open Lamp protection:</u> The regulated open lamp voltage is proportional to the C14 and C13 ratio. C13 has to be rated at 3kV and is typically between 5 to 22pF. The value of C14

is set by the customer to achieve the required open lamp voltage detection value.

$$C14 = C13 \times 1.18 \times V_{(MAX)} rms$$

The value of bias resistor R8 is typically  $100k\Omega$  (not critical).

#### Pin 2 (LI), R2:

<u>Lamp Current Regulation</u>: The R2 is used for feedback to the LI pin to regulate the lamp current. The value for R2 is calculated as 1.33V divided by the lamp rms current (assuming  $V_{ABRT}$  is greater than 1.2V). For RMS 6mA lamp current, R2 value is 220 $\Omega$ .

#### Pin 6 (FT), C2:

The C2 is used to set the fault timer. This capacitor will determine when the chip will reach the fault threshold value.

Open Lamp Time Out:

$$C2(nF) = \frac{t_{OPENLAMP} \times 1\mu A}{1.2V}$$

For a C2 = 820nF, then the time out for open lamp will be 0.98 sec.

<u>Secondary Overcurrent Timeout</u>: When the MP1038 is regulating secondary overcurrent (SI feedback), the source current in the Fault Timer (FT) cap is approximately 55uA. This causes the SI timeout to be about 1/55 of the Open Lamp (LV) timeout. To reduce the SI timeout further, modify the network at the FT pin as shown in Figure 3.

#### Figure 3—Timout Adjustment

For a C2B = 10nF, then the time out for secondary short will be 0.2ms.

Note: The open lamp time out will remain the same value as defined by C2A.

#### Pin 7 (LCS), R3:

R3 is used to set the lamp operating clock. The value for R3 is calculated by

$$R3 = \frac{5e^9}{fo}$$

For R3 =  $100k\Omega$ , operating clock will be 50kHz.

#### Pin 8 (LCC):

This is lamp clock control compensation pin and needs a lag lead lag capacitor/resistor network.

#### Pin 9 (BRC):

This is burst rate control compensation pin and needs a lag lead lag capacitor/resistor network.

#### Pin 4 (COMP), C1:

C1 is feedback compensation capacitor that connects between COMP and AG. A 1.5nF or 2.2nF cap is recommended. This cap should be X7R ceramic. The value of C1 affects the soft-on rise time and soft-off fall time.

#### Pin 14 (Lamp OK), R7:

Lamp OK (LOK) is a normally high logic signal. If a fault occurs, the signal will go low. The R7 is a pull-up resistor connected between a logic high and the LOK pin. If SI or LV voltage trips the fault timer this pin will go low. A  $10k\Omega$  or greater is recommended for this resistor.

# Pin 15 (PRR), Pin 21 (PGR), Pin 22 (PRL), Pin 28 (PGL):

These pins are used to sense the voltages across the external power transistors. These voltages are used by the MP1038 to protect the power transistors in the event of an accidental short from the output of the bridge to ground or the positive rail. It also detects the zero crossings of the AC current in the primary of the power transformer. PRR and PRL should make a Kelvin connection to the drains of the highside power MOSFETs in the output bridge. PGR and PGL should make a Kelvin connection to the sources of the low-side power MOSFETs in the output bridge.

#### Pin 18 (OUTR), Pin 25 (OUTL), C12, R9:

OUTR and OUTL pins are used to sense the voltage at the output of the full bridge. They also are the point of access for the output dampers. OUTR and OUTL should make a Kelvin connection to the sources of the high-side MOSFETs and the drains of the low-side MOSFETs in the output bridge.

The primary transformer current flows through capacitor C12. Its value is typically  $2.2\mu$ F.

This capacitor should be ceramic and has a ripple current rating greater than the primary current. It is more optimal to use two parallel 1µF ceramic caps for minimal ESR losses. R9 is used to ensure that the bridge outputs are at 0V prior to startup. Typically R9 =  $1k\Omega$ .

#### Pin 16 (BTR), Pin 23 (BTL), C8, C10:

BTR and BTL are the bias supplies for the level shift of the upper MOSFETs. C8 and C10 should be 22nF and made of X7R ceramic material.

#### Pin 19 (VCCR), Pin 26 (VCCL), C9, C11:

These capacitors bypass the 5V gate supply for the low-side switches. They also supply power to the MP1038. These pins should be bypassed with a  $0.47\mu$ F ceramic X7R capacitor.

IMPORTANT–For All Applications, VCCR and VCCL must be connected together.

#### Pin 13 (ENSYNC):

ENSYNC is a composite of the Enable and the Burst Oscillator Synchronization function. This pin will enable and disable the chip when the enable function is used.

To synchronize the Burst Oscillator to an external signal, remove R6 from BRS pin and apply a 1 $\mu$ s to 10 $\mu$ s pulse with a falling edge trigger and a repetition rate of 200Hz. The Burst Oscillator will then be synchronized with this signal and start a burst on its falling edge.

#### Pin 11 (DBRT):

This pin is used for burst brightness control. The DC voltage on this pin will control the burst percentage on the output. The signal is filtered for optimal operation. A voltage ranging from 0 to 1.2V on DBRT will correspond to a Burst Duty Cycle of 10% to 100% respectively.

For direct Pulse Width Modulation of the burst signal, connect BRS to VCC and connect DBRT with a logic level PWM signal. A logic High is Burst On and a logic Low is Burst Off.

#### Pin 10 (BRS): C7, R6:

BRS is used to set the Burst Repetition Rate. C7 and R6 will set the burst repetition rate and the minimum burst time:  $t_{MIN}$ . Set  $t_{MIN}$  to achieve the minimum required system

## PRELIMINARY RELEASE - MPS CONFIDENTIAL

brightness. Ensure that  $t_{\mbox{\scriptsize MIN}}$  is long enough that the lamp does not extinguish.

These values are determined as follows:

Select a Minimum Duty Cycle,  $\mathsf{D}_{\text{MIN}},$  where:

$$D_{MIN} = t_{MIN} \times f_{Burst}$$

$$\mathsf{D}_{\mathsf{MIN}} = \frac{\mathsf{t}_{\mathsf{FALL}}}{(\mathsf{t}_{\mathsf{FALL}} + \mathsf{t}_{\mathsf{RISE}})}$$

If operating in Free-Running mode:

$$R6 = \frac{\left[\frac{\left(\frac{1}{D_{MIN} - 1}\right)Vbg}{\gamma + \left(\frac{Vp + Vv}{2}\right)}\right]}{Ib}$$

$$R6 \sim 9.88k \left(\frac{1}{D_{MIN} - 1}\right) + 10k$$

For  $D_{MIN} = 0.1$  and R6 = 176k

$$C7 = \frac{1 - D_{MIN}}{fb \times R6 \times \gamma}$$

For  $D_{MIN} = 0.1$ , R6 = 176k, fb = 200Hz, then C7 = 63nf

$D_{MIN}$  = Minimum Burst Duty Cycle Vbg = Vp - Vv (~1.2V)

Vp = peak BRS voltage (~3.6V)

Vv = valley BRS voltage (~2.4V)

$$\gamma = \ln\left(\frac{3}{2}\right) \approx 0.405$$

Ib = BRS sink current (~160µA) fb = burst repetition rate

If operating in Synchronous mode:

$$C7 = \frac{Ib \times t_{MIN}}{Vbg}$$

t<sub>MIN</sub> = Minimum Burst Time

# **PACKAGE INFORMATION**

**NOTICE:** MPS believes the information in this document to be accurate and reliable. However, it is subject to change without notice. Contact MPS for current specifications. MPS encourages users of its products to ensure that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS cannot assume any legal responsibility for any said applications.